Multimedia Gallery

Demonstrating 3D integration on a massive scale

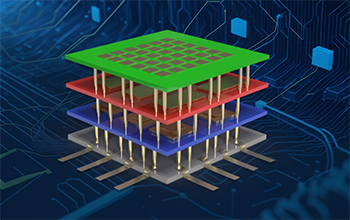

In this rendering, researchers at Penn State demonstrated 3D integration -- vertically stacking multiple layers of semiconductor devices to pack more silicon-based transistors onto a computer chip -- on a massive scale, enabling more energy-efficient computing.

[Research supported by U.S. National Science Foundation grant ECCS 2042154.]

Learn more in the Penn State news story Integrating dimensions to get more out of Moore’s Law and advance electronics. (Date of image: 2024; date originally posted to NSF Multimedia Gallery: March 8, 2024)

Credit: Elizabeth Flores-Gomez Murray/Materials Research Institute, Penn State

Images and other media in the National Science Foundation Multimedia Gallery are available for use in print and electronic material by NSF employees, members of the media, university staff, teachers and the general public. All media in the gallery are intended for personal, educational and nonprofit/non-commercial use only.

Images credited to the National Science Foundation, a federal agency, are in the public domain. The images were created by employees of the United States Government as part of their official duties or prepared by contractors as "works for hire" for NSF. You may freely use NSF-credited images and, at your discretion, credit NSF with a "Courtesy: National Science Foundation" notation.

Additional information about general usage can be found in Conditions.

Also Available:

Download the high-resolution PNG version of the image. (1.3 MB)

Use your mouse to right-click (Mac users may need to Ctrl-click) the link above and choose the option that will save the file or target to your computer.